一、PCB布局布线的建议的意义

PCB布局布线的建议是一个高附加值的任务,它的目的在于完成高EMC性能PCB 设计,同时将由于EMC问题而产生的PCB布局布线成本最小化。PCB布局布线的建议 的核心包括以下三方面:

l 指出关键EMC器件的在PCB中的相对位置;

l 指岀PCB中哪些区域需要进行完整的地平面设计,并将该地平面的阻抗最小化;

l 串扰防止的处理。

它的具体内容包括两方面:

l 书面的建议描述;

l PCB布局布线建议示意图。

完成PCB布局布线建议后,在电子工程师将原理图送到CAD小组进行布局布线设计 前,EMC专家需要与CAD的专家和工程师进行充分的沟通,将所需表达的意见充分传 达给CAD的专家和工程师。

二、PCB层数及各层的分配

从EMC方面考虑,除非2层板也能设计出较为完整地平面,否则最好采用带有地层 和电源层的4层以上的PCB。实践证明,4层板与2层板相比,4层板能取得高于2层板 100%的EMC性能。但要注意:4层板以上,并非层数越多越好。2层板通常地平面很难 设计完整,如果使用2层板,那么工程师要特别注意地平面的设计。

PCB层排布的一般原则:

l 元件面下面(第2层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;

l 所有信号层尽可能与地平面相邻;

l 尽量避免两信号层直接相邻;

l 主电源尽可能与其对应地相邻。

4层PCB层的层排布方式见表

| 方案 | 电源层数 | 地层数 | 信号层数 | 1 | 2 | 3 | 4 |

| 1 | 1 | 1 | 2 | S | G | P | S |

| 2 | 1 | 1 | 2 | G | S | S | P |

| 3 | 1 | 1 | 2 | S | P | G | S |

方案1为4层PCB的主选层设置方案,在元件面下有一地平面,关键信号优选布TOP层。至于层厚设置,有以下建议:

•满足阻抗控制。

•芯板(GND到POWER)不宜过厚,以降低电源、地平面的分布阻抗;保证电源平面的去耦效果。为了达到一定的屏蔽效果,有人试图把电源、地平面放在TOP、BOTTOM层,即采

用方案2。用此方案往往是试图达到想要的屏蔽效果,但至少存在以下缺陷:

•电源、地相距过远,电源平面阻抗较大。

•由于元件焊盘等影响,电源、地平面极不完整。

•由于参考面不完整,信号特性阻抗不连续。

实际上,对于PCB中器件越来越密的情况下,本方案的电源、地几乎无法作为完整的参考平面,预期的屏蔽效果很难实现。方案2的使用范围有限。但在个别单板中,方案2不失为最佳层设置方案。

方案3同方案1类似,适用于主要器件在BOTTOM布局或关键信号底层布线的情况;一般情况下,限制使用此方案。

6层PCB层的层排布方式见表

| 方案 | 电源 | 地 | 信号 | 1 | 2 | 3* | 4 | 5 | 6 |

| 1 | 1 1 | — 1 |

4 | S1 | G | S2 | S3 > | P | S4 |

| 2 | 1 | 1 | 4 | S1 | S2 | G | P | S3 | S4 |

| 3 | 1 | 2 | 3 | S1 | G1 | S2 | P | G2 | S3 |

| 4 | 1 | 2 | 3 | S1 | G1 | S2 | G2 | P | S3 |

对于6层板,优先考虑方案3,优选布线层S2,其次S3、S1。主电源及其对应的地布在4、5层,层厚设置时,增大S2〜P之间的间距,缩小P〜G2之间的间距(相应缩小G1〜S2层之间的间距),以减小电源平面的阻抗,减少电源对S2的影响。

在成本要求较高的时候,可采用方案1,优选布线层SI、S2,其次S3、S4,与方案1 相比,方案2保证了电源、地平面相邻,减少电源阻抗,但SI、S2、S3、S4全部裸露在 外,只有S2才有较好的参考平面。对于局部、少量信号要求较高的场合,方案4比方案3更适合,它能提供极佳的布线 层S2。

8层PCB层的层排布方式

| 方案 | 电源 | 地 | 信号 | 1 | 2 | 3 | 4 . | 5 j | 6 | 7 | 8 |

| 1 | 1 | 2 | 5 | S1 | G1 « | S2 | 'S3 ; | P | S4 | G2 | S5 |

| 2 | 1 | ,3 | 4 | S1 | - G1 | S2 | G2 - | P ” | S3 . | G3 1 | 'S4 -1 |

| 3 | 2 | 2、 | :4.. | S1 . | ;G1 | S2 | P1 | G2 | S3 . | P2 R | S4 |

| 4 | 2 | 2 | 4 | S1 : | G1 | S2 | P1 | P2 | S3 , | G3 | S4 |

| 5 | 2 | 2 | 4 | S1 | G1 | P1 | S2 | S3 | G2 | P2 | S4 |

对于单电源的情况下,方案2比方案1减少了相邻布线层,增加了主电源与对应地相邻,保证了所有信号层与地平面相邻,代价是牺牲一布线层;对于双电源的情况,推荐采 用方案3,方案3兼顾了无相邻布线层、层压结构对称、主电源与地相邻等优点,但S4 应减少关键布线;方案4无相邻布线层、层压结构对称,但电源平面阻抗较高,应适当加 大3〜4、5〜6之间层间距,缩小2〜3、6〜7之间层间距;方案5与方案4相比,保证了 电源、地平面相邻,但S2、S3相邻,S4以P2作参考平面,对于底层关键布线较少以及S2、S3之间的线间串扰能控制的情况下此方案可以考虑。

三、地平面和电源平面在PCB层中的位置

层的放置以电快速瞬变脉冲群测试原理为基础,通过对共模电流流向的分析来确定。

对于浮地设备来说,大多数情况下,可以把GND层当成是屏蔽层,用来泄放共模干扰电 流,AGND必须放置在没有被共模干扰耦合到的层和位置。(注:这里描述的AGND通 常为产品中的模拟电路,其电平较低,噪声容限较低,较容易受干扰。)

PCB电源的层数由其电源种类数量决定。对于单一电源供电的PCB, 一个电源平面足够 了;对于多种电源,若互不交错,可考虑采取电源层分割(保证相邻层的关键信号布线不跨 分割区);对于电源互相交错(尤其是像8260等IC,多种电源供电,且互相交错)的单板, 则必须考虑采用2个或2个以上的电源平面,

每个电源平面的设置需满足以下条件:

l 单一电源或多种互不交错的电源;

l 相邻层的关键信号不跨分割区。

地的层数除满足电源平面的要求外,还要考虑:

l 元件面下面(第2层或倒数第2层)有相对完整的地平面;

l 高频、高速、时钟等关键信号有一相邻地平面。

l 关键电源有一对应地平面相邻。

四、指出敏感元器件在PCB中放置的相对位置

敏感元器件一般放置在电路板的当中位置,并且在PCB中没有耦合的层上,例如图&10 中,信号及元件面1为没有耦合的面,这一层中没有共模电流流过。信号及元件面2为存在共 模电流耦合的层,这一层中共模电流会流过,自然器件置于该层中,将受更严重的干扰。

五、滤波电容等滤波器件在PCB中的相对放置

滤波电容通常放置在被滤波器件的相应管腿附近,或在共模电流泄放的路径中。所有 的滤波电容的连接不能用长线的方式,而要保证低阻抗的连接,比较好的做法是,滤波电容引线长宽比小于3,至少要做到小于5。

六、地平面的设计

共模电流流过的区域必须具有完整的地平面,完整地平面意味着一块没有任何过孔、 开槽、裂缝且长宽比小于3的PCB铜箔。以下几个地方通常需要使用完整地平面:

(1)共模电流的泄放路径上;

(2)有共模电流流过的两个器件的地管腿之间; ⑶ 端口上的滤波器电容、芯片去耦电容、旁路电容与地之间的互连线。

为了更好地实现PCB中的完整地平面设计,建议在PCB布局确定后,先将所需要的

完整地平面布置好,并将需要进行完整地平面设计的区域设定为不能有任何过孔、开槽、 裂缝等的区域,然后进行印制线布线设计。这样可以防止先把印制线布置好后,发现某区 域的地平面不完整,而再进行修改带来的时间浪费(通常这个时候再进行修改,难度也会 增加)。(注:当共模电流流过GND时,并不是整个PCB的GND平面需要完整地平面,这也

是不可行的,只是在以上3点描述的地方需要完整地平面。)

七、模拟地地平面的设计

这里所述的模拟地AGND通常是产品中电平较低、对干扰比较敏感的电路的参考地。该平面必须设计在既没有共模耦合、也没有共模电流流过的位置上。如果没有办法避免共 模电流流过AGND,那么共模电流流过的路径必须为完整地平面(完整地平面意味着一 块没有任何过孔、开槽、裂缝且长宽比小于3的PCB铜箔)。

八、电源平面的设计

电源是产品电路的主电源,该平面通常在保证没有串扰发生的情况下尽可能大。 并且VCC平面尽量做到与GND地平面邻近,以增加电源平面与地平面之间的层间电容, 这对高频去耦有效。

九、串扰防止的处理方式

“脏”(红色)的信号线、特殊处理的时钟信号线、高速信号线(特殊颜 色)与“干净”(绿色)信号线之间必须考虑串扰问题,处理串扰的方式一般有:

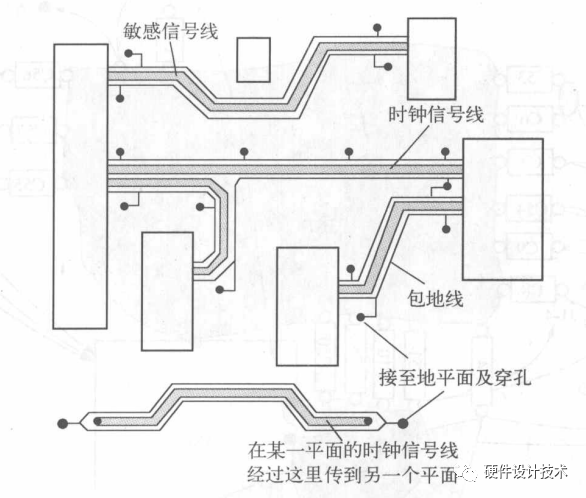

l 对信号线进行包地(图8-11)处理,在互为串扰的信号线之间插入地线。

l 把信号线分布在不同的层中,其间有GND地层隔离。同一层中左右布置且没有 包地、相邻层的上下平行布置,都认为存在串扰。

l 信号线下方必须有地平面。

十、特殊信号线(如时钟信号线、高速信号线、敏感信号线等)的处理方式

给出表列出的时钟信号线、敏感信号线、高速信号线等的布线注意方法,包括阻抗匹配、串扰等。始端阻抗匹配的电阻和限流电阻通常放置在信号发出端。在 串扰处理上,除了考虑这些信号线在PCB中的具体位置之外,通常还应釆用屏蔽地线包地的方式处理。

十一、PCB中空置区域的处理

所有空置区域都要铺铜处理,并将其通过适量过孔与相应区域的地平面相连。

十二、其他建议

列出其他建议。

PCB布局布线示意图

画出PCB布局布线示意图是为了更直观地表达以上PCB布局布线的建议,并把一些 用文字很难清楚表达的建议用示意图的方式表示出来。它所包含的内容是为了让CAD专 家和工程师更容易理解。一般在该PCB布局布线示意图中,将表达出完整地平面(没有 过孔、开槽、裂缝,长宽比小于3)在PCB中及与器件的相对位置,I/O端口上的滤波电 容、器件的去耦电容与器件、完整地平面的相对位置,及“脏”信号线、“干净”信号线。

PCB设计审查与EMC风险评估

一、PCB设计审查的意义和任务

PCB审查的目的是为了检查PCB设计者是否将EMC专家给出的PCB布局布线建议 落实。纵然将全部PCB布局布线的建议都落实会有很大的困难,但是通过审查,EMC专 家与CAD的专家一起能找到一种比较折中的方法,这种折中的方法,不但能使EMC风 险降低,而且还能顺利实现PCB布局布线。在PCB审查结果中,EMC专家需要把一些 未落实的或实际实现与建议不一致的现象一一列出,这将有助于产品在EMC测试时定位 分析。列出的内容主要包括如下3个方面:

l 共模电流流过路径上的阻抗,如地平面是否完整,是否没有任何过孔、裂缝

l 和开槽。.'

l “脏”信号印制线及一些需要进行特殊处理的信号印制线与其他信号线之间是否 存在串扰。

l 去耦、旁路电容和滤波电容位置是否合理,引线阻抗是否足够低。

二、地平面完整性及其阻抗审查

(1)如果地平面的设计没有按照PCB布局布线的建议执行,那么按表所示的格式 指出不同点,并说明风险在哪里。

| 序 号 | 原建议描述 | 实际处理方式 | 风险点描述 |

| 1 | |||

| 2 | |||

| 3 |

(2)对有可能出现风险的点,按表所示的格式列出可行的修改建议。

| 序 号 | 可行的修改建议 |

| 1 | |

| 2 | |

| 3 |

三、串扰审查

(1)如果串扰防止设计没有按照PCB布局布线的建议执行,那么按表所示的格 式指出不同点,并说明风险在哪里。

| 序 号 | 原建议描述 | 实际处理方式 | 风险点描述 |

| 1 | |||

| 2 | |||

| 3 |

(2)对有可能出现风险的点,按表所示的格式列出可行的修改建议。

| 序 号 | 可行的修改建议 |

| 1 | |

| . 2 | |

| 3 |

四、去耦、旁路电容和滤波电容的审查

是否将PCB布局布线建议中关于去耦一旁路一滤波电容的建议落实?若有不同的地

方,那么:

(1)如果去耦一旁路电容和滤波电容在PCB中设计(主要是去耦电容的位置是否靠 近被去耦器件电源管脚,并保证引线阻抗足够低,如引线长宽比小于3;旁路电容位置是

否在共模电流泄放的最佳位置上,并保证引线阻抗足够低,如引线长宽比小于3;滤波电 容是否放置在I/O端口上,同时在共模电流泄放的最佳位置上,并保证引线阻抗足够低, 如引线长宽比小于3)没有按照PCB布局布线的建议执行,那么按表所示的格式指出不同点,并说明风险在哪里。

| 序号 | 电容代号 | 原建议描述 | 实际处理方式 | 风险点描述 |

| 1 | ||||

| 2 | ||||

| 3 | ||||

| 4 |

(3)对有可能出现风险的点,按表所示的格式列出可行的修改建议。

| 序号 | 电容代号 | 可行的修改建议 |

| 1 | ||

| 2 | ||

| 3 |

五、PCB布局布线文件

为了保持完整性,建议把PCB布置图分层列出,图X〜图X是按图Y所示的设计建议所完成的PCB布置图的实例。