热拔插系统必须使用电源缓启动设计,热拔插系统在单板插入瞬间,单板上的电容开始充电。因为电容两端的电压不能突变,会导致整个系统的电压瞬间跌落。同时因为电源阻抗很低,充电电流会非常大,快速的充电会对系统中的电容产生冲击,易导致钽电容失效。

如果系统中采用保险丝进行过流保护, 瞬态电流有可能导致保险丝熔断, 而选择大电流的保险丝会使得在系统电流异常时可能不熔断,起不到保护作用。所以,在热拔插系统中电源必须采用缓启动设计,限制启动电流,避免瞬态电流过大对系统工作和器件可靠性产生影响。

1、LDO

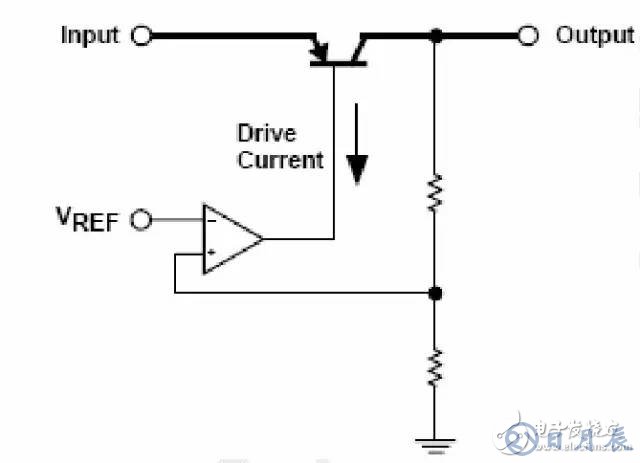

在压差较大或者电流较大的降压电源设计中,建议采用开关电源,避免使用 LDO采用线性电源(包括 LDO)可以得到较低的噪声,而且因为使用简单,成本低,所以在单板上应用较多。FPGA 内核电源、某些电路板上射频时钟部分的电源等都使用线性电源从更高电压的电源上调整得到。线性电源的基本原理如图所示。

输出电压经过采样后和参考电源(由晶体管带隙参考源或者齐纳二极管提供)进行减法运算,差值经过放大后控制推动管上的电压降V dropout =V output -V input , 使得当 V input 变化或者负载电流变化导致 V output 变化时,通过 V dropout 的变化保证 V output 的稳定。

由图中可见,负载电流全部流过调整管,而输入电压和输出电压之间的差异全部都加在调整管上。调整管上耗散的功率为 V dropout *I。当电压差较大时,或者负载电流较大时,稳压器将承受较大的功率耗散。

LDO必须计算热耗并满足降额规范另外,输入的电源提供的功率为 V input *I,即采用线性电源时电源功率的计算不能使用负载电压和电流的乘积计算,必须采用线性电源输入电压和负载电流的乘积计算采用线性电源时电源功率的计算不能使用负载电压和电流的乘积计算,必须采用线性电源输入电压和负载电流的乘积计算。必须经过计算和热仿真确保系统的正常工作。

例如采用 1 只 TO-263 封装的 LDO 将电压从 3.3V 降到 1.2V,负载电流为 1.5A,负载上耗散的功率为 1.8W。此时 LDO 上承担了 2.1V 压降,耗散的功率 3.15W,3.3V 电源提供的功率为 4.95W!封装的热阻约为 40℃/W,则如果不采取任何散热措施,则温升能够达到约 120℃。对 LDO 必须通过热仿真确定合适的散热措施,并且在 3.3V 电源在预算中必须能够提供 1.5A 的电流(或者 5W 以上的功率) ,保证系统的工作正常。采用开关电源能够达到很高的效率,对大电流及大压差的场合,推荐采用开关电源进行转换。如果电路对纹波要求较高, 可以采用开关电源和线性电源串联使用的方法, 采用线性电源对开关电源的噪声进行抑制。

2、LDO 输出端滤波电容选取时注意参照手册要求的最小电容、电容的 ESR/ESL 等要求确保电路稳定。推荐采用多个等值电容并联的方式,增加可靠性以及提高性能DO 输出电容为负载的变化提供瞬态电流,同时因为输出电容处于电压反馈调节回路之中,在部分 LDO 中,对该电容容量有要求以确保调节环路稳定。该电容容量不满足要求,LDO 可能发生振荡导致输出电压存在较大纹波。多个电容并联,以及对大容量电解电容并联小容量的陶瓷电容,有利于减少 ESR 和 ESL,提高电路的高频性能,但是对于某些线性稳压电源,输出端电容的 ESR 太低,也可能会诱发环路稳定裕量下降甚至环路不稳定。

3、滤波电容

(1) 电源滤波可采用 RC 、LC 、π 型滤波。电源滤波建议优选磁珠,然后才是电感。同时电阻、电感和磁珠必须考虑其电阻产生的压降对电源要求较高的场合以及需要将噪声隔离在局部区域的场合, 可以采用无源滤波电路。在采用无源滤波电路时,推荐采用磁珠进行滤波。磁珠和电感的主要区别是,电感的Q值较高,而磁珠在高频情况下呈阻性,不易发生谐振等现象。

电感加工精度较高,而磁珠加工精度相对较低,成本也较便宜。在选择滤波器件时,优选磁珠。选择电阻和电容构成无谐振的一阶 RC 低通滤波器,但是该电路只能应用于电流很小的情况。负载电流将在电阻上形成压降,导致负载电压跌落。无论是采用何种滤波器,都需要考虑负载电流在电感、磁珠或者电阻上的压降,确认滤波后的电压能够满足后级电路工作的要求。

例如在某单板锁相环路设计中采用了一阶 RC 滤波器,滤波电阻选择12 欧姆。锁相环中 VCXO 的工作电流约为 30mA,在滤波电阻上产生 300mV 的压降,额定电压 3.3V的 VCXO 实际工作电压只有不到 3V,易发生停振等现象。在某光口子卡上,发生过某型号光模块当光纤插上时 SD(光检测)信号上升缓慢,不能正确反映实际情况的问题。

经过检查发现滤波电感的直流电阻约为 3 欧姆, 光模块工作电流约为 100mA, 电感上的压降导致光模块的工作电压只有约 2.9V 左右,在该型号光模块上会出现 SD 上升缓慢的故障。另外,对于滤波电路,应保证电感、磁珠或者电阻后的电容网络能够保证关心的所有频率下,都能够保证低阻抗。必要时应采用多种容量的电容并联,并局部铺铜的方式达到目标阻抗。(参见时钟驱动芯片滤波电路设计部分)。在某单板上,采用了磁珠和 0.1u 电容为时钟驱动芯片提供滤波。经过测试,时钟驱动芯片管脚上的纹波高达 1V 以上。采用多电容并联的方式可以有效地为时钟芯片提供去耦。

(2)大容量电容应并联小容量陶瓷贴片电容使用

大容量电容一般为电解电容,其体积较大,引脚较长,经常为卷绕式结构(钽电容为烧结的碳粉和二氧化锰) 。这些电容的等效串联电感较大,导致这些电容的高频特性较差,谐振频率大约在几百 KHz到几 MHz 之间(参见 Sanyo 公司 OSCON 器件手册和 AVX 公司钽电容器件手册) 。

小容量的陶瓷贴片电容具有低的 ESL 和良好的频率特性,其谐振点一般能够到达数十至数百 MHz(参见参考文献《High-speed Digital Design》以及 AVX 等公司陶瓷电容器件手册) ,可以用于给高频信号提供低阻抗的回流路径,滤除信号上的高频干扰成分。因此,在应用大容量电容(电解电容)时,应在电容上并联小容量瓷片电容使用。

(3)输入电容

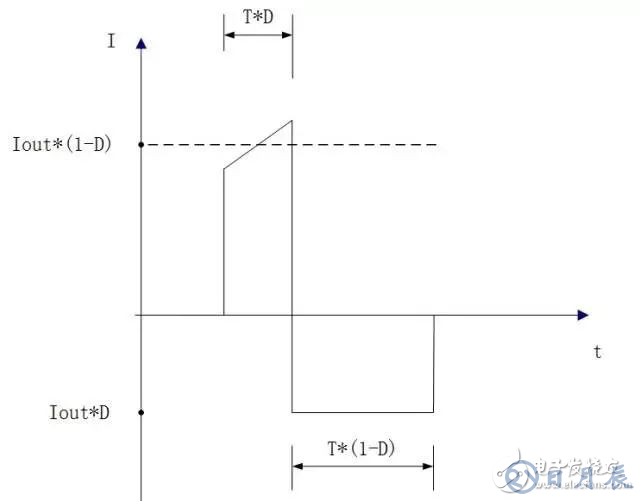

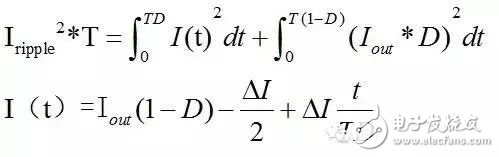

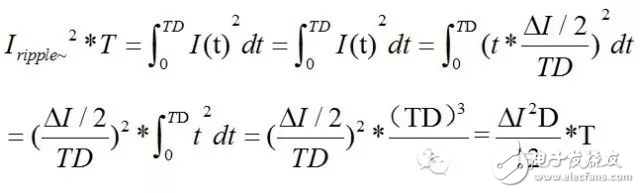

计算输入电容的纹波电流,这个推导的过程,利用到积分公式。通过分析和推导,可以对电路的工作原理有比较透彻的理解。如果考虑输出纹波电流。那么电容上的纹波电流的波形为:

由于在上管打开的阶段,输入电流的大小即可近似的看成输出电流的大小。所以只需要将输出电流的波形叠加在输入电容的波形上面,可以得到上图中的波形。

那么按照有效电流定义,我们可以通过对电流平方在时间上的计算

为了简便计算,我们将能量拆成纹波部分,和直流部分。原先的直流部分,我们直接用乘法进行计算。直流部分,我们按照近似计算的方法可以得到。交流部分的功耗,我们按照公式计算可以得到:

所以总的电容上的有效电流为:

如果选用220uF的电容,每个能承受的有效电流为3.8A。。如果我们计算出来输入电容的有效电流值为7A,则需要选用220uF电容2个。高分子电解电容能够承受的有效电流值是有限的。在设计时需要充分考虑电容的承受能力。

4、升压电路

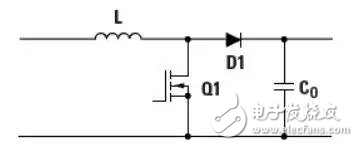

升压电源(BOOST)使用必须增加一个保险管以防止负载短路时,电源直通而导致整个单板工作掉电。保险的大小由模块的最大输出电流或者负载最大电流而定升压电源(Boost)的基本拓扑如下图所示:

当 Q1 导通时两端电阻很小, 电源电压加在 L两端,电能转化为磁场存储在 L 中,此时 D1 截止,避免 C0 上的电压向 Q1 流动。当 Q1 关断时,L 中的电流不能突变,电源和 L 一起通过 D1 向C0 充电并向负载供电,得到一个高于输入电压的输出电压。由图中拓扑可以看出,我们不能通过控制 Q1 的通断来切断输入和输出之间的通路或者控制输出电流。当输出电源短路时,输入电源(一般是单板主电源)通过 L 和 D1 直接短路到地。导致的结果将是L 或者 D1 烧毁且失效模式为开路。在 L 或者 D1 烧毁之前,单板电源处于短路状态,如果 L 和 D1 电流降额较大,可能导致单板电源保护而不能上电。为了避免上述问题, 建议为升压电源添加一个保险管防止负载短路, 保险的大小依照模块的最大输出电流或者负载的最大电流而定。

5、防反接

电源要有防反接处理,输入电流超过 3A于 ,输入电源反接只允许损坏保险丝;低于或等于 3A,输入电源反接不允许损坏任何器件电源要有防反接处理,输入电流超过 3A,输入电源反接只允许损坏保险丝;低于或等于 3A,输入电源反接不允许损坏任何器件。回路电流较大时,直流电源反接处理可以按照以下方法处理。原理图如下所示:

直流电源正常接入时, 光耦D1由于输入二极管反偏置, 所以输出C-E不能导通, 这时并联的NMOS管将由于 G-S 电压的稳压至 12V,使 D-S 导通。这样电源回路将能顺利形成。电容 C1 是起到缓启动作用的,这样可以起到防浪涌的目地。电阻 R6、二极管 VD3 构成电容 C1 的放电回路。当电源反接的时候,由于光耦输入二极管正偏置,输出 C-E 导通,使并联的 NMOS 管截止。这样回路就切断了,起到了防反接保护的作用。由于并联 NMOS 管的 R DS 比较小,损耗小,比较适合于低压大电流的场合。回路电流较小时,可以直接在输入回路中串联二极管。反接时,由于二极管的单向导电性,电源被阻断。

6、电感

禁用磁饱和电路;禁止选用采用磁饱和电路的电源模块禁用磁饱和电路,因为:a、磁饱和电路因为所用磁环的原因对温度比较敏感,易在高温工作时不稳定。b、动态负载能力差,在磁饱和路负载最小时工作最恶劣,易形成输出不稳定。

7、上电时序

1. 对于多工作电源的器件,必须满足其电源上掉电顺序要求

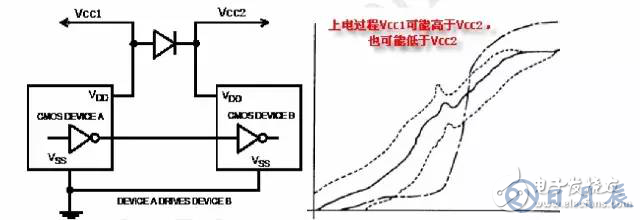

对于有核电压、IO 电压等多种电源的器件,必须满足其上电和掉电顺序的要求。这些条件不满足,很有可能导致器件不能够正常工作,甚至触发闩锁导致器件烧毁。例如 TMS320C6414T 型 DSP,2005年 5 月之后的 Errata 中说明,当 DVDD 较 CVDD 早上电时,可能出现 PCI/HPI 数据错的问题。对于QDR、DDR 内存,其上电顺序也有要求,否则可能导致闩锁,造成器件烧毁的后果。当有多个电源时, 如必要可采用专用的上电顺序控制器件确保上电顺序。设计中应保证在器件未加载烧结文件时,电源处于关断状态设计中应保证在器件未加载烧结文件时,电源处于关断状态。也可以通过在不同的电源之间连接肖特基二极管确保上电掉电过程中不会违反上掉电顺序要求。

因为电源模块、 电源上的电容都会对电源上电顺序产生影响, 可能出现上电过程中违反电压要求的情况,如上右图所示,所以必须进行测试验证。

2、 多个芯片配合工作,必须在最慢上电器件初始化完成后开始操作当多个芯片配合工作时, 必须在最慢的期间完成初始化后才能开始操作, 否则可能造成不可预料的结果。

例如 LVT16244 驱动器具有上电 3 态功能,即使 OE 端被下拉到地,也需要等到电源电压上升到一定阈值才会脱离高阻态, 而此前 EPLD 等器件可能已经开始工作, 这样就可能导致 EPLD 读到错误的状态。参见前面的说明。对于某些 ROM 等器件,在上电后一段时间才能开始工作,如果在此之前就开始读取,也可能导致数据错误。

8、PCB设计

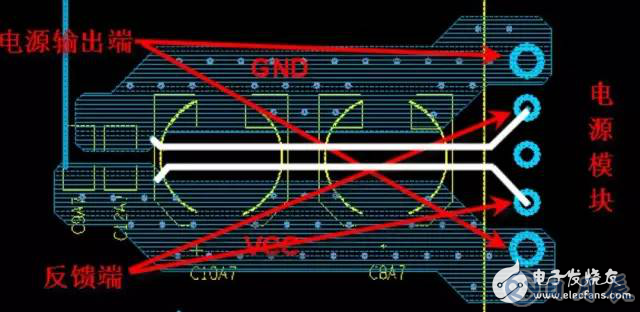

1、 电源模快/ 芯片感应端在布局时应采用开尔文方式很多电源模块和电源芯片在设计时,采用了独立的 Sense 管脚,作为对输出电压的反馈输入。这个Sense 信号应该从取用电源的位置引给电源模块,而不应该在电源模块输出端直接引给电源模块,这样可以通过电源模块内部的反馈补偿掉从电源模块输出传输到实际使用电源处路径带来的衰减。如下图中白色走线所示。

对于电源监控电路等,也应该遵守相同的原理,即从实际需要监控点将电源引给监控电路,而不是从监控电路最近处引给监控电路,以确保精确性。

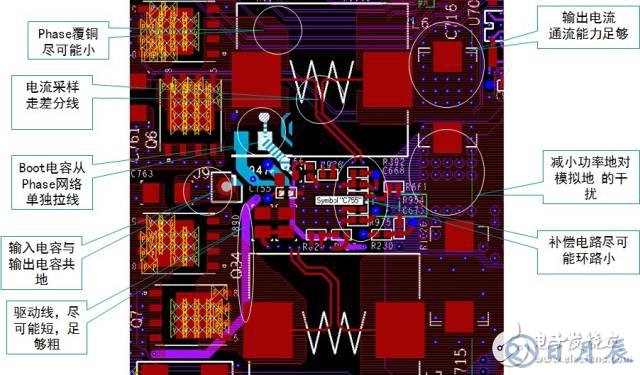

2、Buck电源PCB设计要点

1、输入电容,输出电容尽量共地;

2、输出电流过孔数量保证通流能力足够,电流为设定的过流值;

3、如果输出电流大于20A,最好区分控制电路AGND和功率地GND,两者单点接地,如果不做区分,保证AGND接地良好;

4、输入电容靠近上管的D极放置;

5、Phase管脚因为其强电流,高电压的特性,辐射大,需做以下处理

a:Phase相连接的上管的S极,下管的D极和电感一端打平面处理,且不打过孔,即尽量保证3者和电源芯片在同一个平面上,且最好放置在top面;

b:Phase平面保证足够的通流能力的前提下,尽量减小面积;

c:关键信号远离该Phase平面;

d:小电流的Phase网络直接拉线处理,禁止拉平面;

6、输入电容的GND,电源输入因为噪声大,敏感信号需远离该平面,遵循3W原则,禁止高速信号在上述地平面打的过孔中间走线,尤其关注背板的高速信号;

7、GATE,BOOT电容走线尽量粗,一般为15mil~40mil;

8、电压采样因为电流小,容易受干扰,如果为近端反馈尽量靠近电源芯片,如果为远端反馈,需走差分线,且远离干扰源;

9、DCR电流采样网络,需要差分走线,整个采样网络尽量紧凑,且需靠近电源芯片放置,温度补偿电阻靠近电感放置;

10、环路补偿电路尽量面积小,减小环路,靠近电源芯片放置;

11、电感下禁止打孔,一方面防止有些电感为金属表层,出现短路;一方面因为电感的辐射大,如果下面打孔,噪声会耦合;

12、MOS管下需打过孔进行散热,过孔数量按照输出最大电流计算,非过流值;

13、电源芯片底部打过孔到背面进行散热处理,覆铜越大散热越好,最好部分亮铜处理;