处理器指令集架构(ISA)的代码密度对在现实世界中的SoC处理器的能耗效率有很大的影响。在选择嵌入式SoC处理器时,功耗和面积通常是主要被考虑的,但另一个主要因素,往往在这样的评估中被忽视了:处理器指令集架构(ISA)的代码密度。

一个紧密的指令集产生较小的代码,导致少取指令。这对于能效有着重大的影响,因为从片上存储器取指令所使用的能耗远远大于CPU执行指令所需的。

大多少? 2010年斯坦福大学詹姆斯·贝尔福的博士论文对高效的嵌入式计算研究表明,对于一个典型的32位RISC处理器,从一个2字节的片上缓存取指令所消耗的能量比一个32位的加法运算(在一个典型的45纳米CMOS制程)多消耗的多6.8倍.

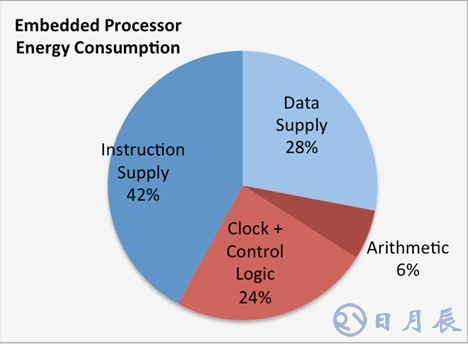

Dally等人的另一项发表在IEEE计算机的研究发现,典型的嵌入式处理器的能耗的42%来自取指,而只有6%的被消耗于执行实际的算术运算。这些研究都使用一个小的片上指令缓存。事实上指令往往更需要访问较大的片上甚至片外存储,那么功耗的影响将被放大, 系数6.8倍将变为50倍或更多。

这里的结论是明确的:使用需要较少指令的ISA,比简单地选择一个执行更有效的处理器在是节能上更有帮助.对一颗CPU而言, 面积(门使用)是另一种处理器选择的常见标准。但SoC为程序存储器所需的面积的要大得多,尤其是对非密集的代码。

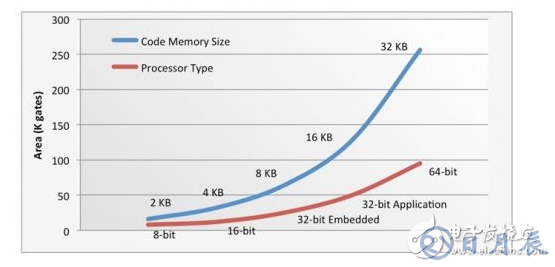

一般法则是约1千比特的片上SRAM占据的面积与1K的逻辑门相同。将此规则应用于一些典型的处理器所得的面积的结果,如图2中曲线所示。 (在这里处理器的面积估计范围从小型8位处理器的8K门到先进的64位处理器的100K门,而适合嵌入式程序的的片上代码存储空间估计范围从2至32千字节。)

此图清楚地表明,对大多数32位嵌入式SoC ,程序存储器是CPU面积的两倍或两倍以上。更为紧凑的代码显然需要更小的程序存储器。因此,在只考虑CPU所需门数的情况下, 选择采用了紧凑ISA的处理器可以显著降低SoC面积。

以上考虑促成了我们所提供的BA22系列的32位处理器内核,其对任何需要考虑低功耗的处理器系统都很有价值。我们相信BA22 ,在同行业中具有最优的代码密度,估计比ARM ?的Thumb- 2 ISA的代码密度最高能有20 %的提升。

有竞争力的性能( 2.1或以上Coremarks/兆赫) ,面积(15K门起), 时钟频率(在65nm - LP 将超过400 MHz)和功率效率(0.02毫瓦/兆赫兹),因为出众的代码密度,使得BA22成为功耗敏感的深嵌入系统CPU IP的最佳选择之一。