功率半导体封装技术探究

1.功率半导体模块的封装结构

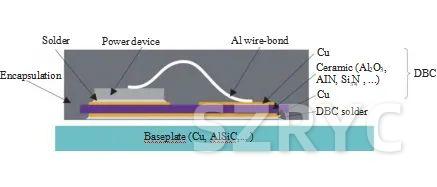

在现代功率半导体产品中,普遍采用覆铜陶瓷(DBC)作为电气绝缘和热传导介质,辅以环氧树脂塑封保护,以承载和散热半导体芯片。DBC基底常用材料包括氧化铝(Al2O3)、氮化铝(AlN)和氮化硅(Si3N4),其中铝基和硅基DBC板在工业应用中最受欢迎。由于第三代半导体如硅碳(SiC)在结温、开关速率以及封装密度方面超越传统硅基器件,要求更高的散热和可靠性,这就促使了新型封装设计的研发,使其适应更高的工作温度。

(1)无键合线单面封装结构

传统的金属键合线封装会增加寄生电感而影响开关特性和可靠性。新型封装结构采用了无键合线设计,利用铜钉替代传统键合线,减少寄生电感并实现互连。此外,使用软硅胶与硬环氧树脂相比较,能减少热循环中的应力,银颗粒烧结替代传统钎料,以实现更优的功率循环寿命和更小的模块体积。

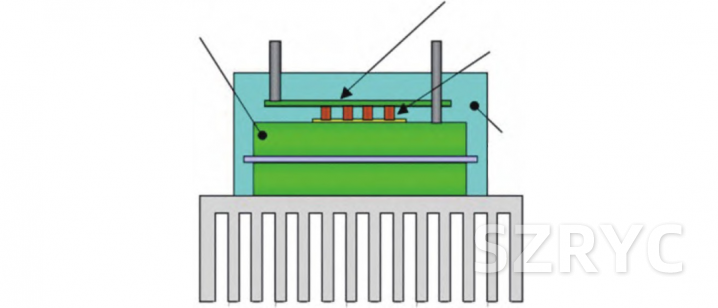

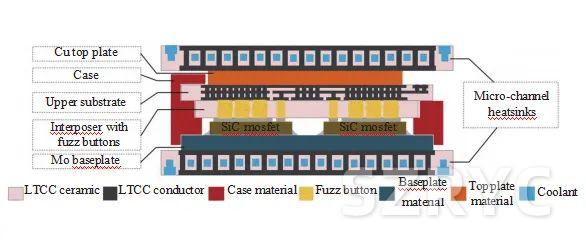

(2)双面散热封装结构

封装结构的进步,如使用液冷等技术,实现了双面散热,有效减少了热阻,提升可靠性。例如,利用微型柔性压针“Fuzz Button”技术或是DBC技术实现芯片的双面散热,这些创新方法都展示了封装结构在散热方面的优化潜力。

(3)多层陶瓷基板堆叠技术

为降低高功率密度设备中的高电场风险,提出使用DBA板替代DBC板,并通过多重层叠与焊接技术减少峰值电场,同时促进更好的散热效果,提升模块的整体性能与效率。

2.芯片贴装技术的革新

新型高温耐用贴装料如金属烧结料替代传统钎料或导电胶,在保持优异导电性和强固接合的同时,承受更高的工作温度和更多的热循环,这为高性能半导体器件如SiC的应用需求提供了解决方案。

3.进阶的引线键合技术

考虑到热膨胀等物理特性,引线材料的选择对模块可靠性有决定性影响。铜因其高电导率及与芯片热膨胀系数的兼容性而越发受到青睐,但铜线连接需要更高的压力和能量。同时,铝铜合金键合线以其优秀的电气性能和适合批量生产的特性,成为一个成本效益高、可靠性强的过渡选择。

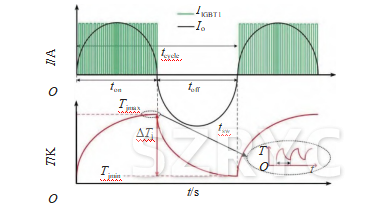

评估功率半导体器件可靠性的功率循环测试探究

电力电子组件的可靠性测试是确保其长期稳定运行的关键。与其他测试方式如温度循环试验相比,功率循环测试能更真实地模拟器件工作状态,通常将器件固定在散热器上,通过周期性电流施加和断开,引发器件结温的周期性变化来模拟器件工作中的温度波动,从而评估其可靠性。

1.功率循环测试的关键技术

(1)测试参数及其控制方法

常用的功率循环测试策略侧重于控制结温变化和最大结温。欧洲AQG 324标准和国内QCT 1136—2020标准提出了秒级和分钟级的划分,来评估不同位置的连接可靠性。电流激励方法包括直流功率循环电路和脉冲宽度调制(PWM)。目前,由于简便性和结温测量准确性,直流方法被广泛采用。

在控制策略方面,严苛性控制策略例如固定电流导通时间ton、壳温变化量、功率损耗和结温变化对测试结果的影响极大。欧洲标准倾向于采用固定ton作为标准控制策略,而国内标准通常保持结温变化一致。此外,结温测量的延迟也对测试结果产生重要影响,需要精确定时以避免误差。

(2)参数监测与失效判别

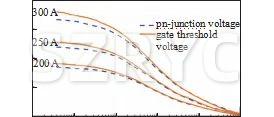

IGBT为例,监测故障模式涉及到热阻和饱和压降的变化。监测技术包括红外相机、热电偶和温敏电参数法等。为了更准确地监测结温,常用温敏电参数法通过测量小电流下的饱和压降和栅极阈值电压,并与已知的温度特性相结合。特别是SiC材料器件,需考虑其固有的阈值电压不稳定性,使用特殊方法来获取准确的结温数据。

2.功率模块失效机理研究

(1)钎料层失效研究

钎料层疲劳失效主要表现为空洞和裂纹,斑点的形成会导致热阻增加,并随着功率循环加剧。研究表明,空洞的形成会影响模块的温度分布。裂纹生长对钎料层热阻有显著影响,研究还针对裂纹的成因、大小、位置进行了深入分析。

(2)键合线失效研究

键合线失效表现为断裂和脱落,是因为温差引起的热应力导致的。VCE作为监控指标,呈现出与键合线裂纹生长具有相似的增长趋势。进一步的研究聚焦于裂纹生长对器件参数的影响。

半导体封装可靠性发展探究

1.提升功率器件的散热能力.发挥高性能功率器件的潜力,提高器件的散热能力是必然趋势。在封装结构方面,设计无键合线的多维散热结构,降低寄生电感、增加散热路径;在材料方面,在不改变整体性能的基础上,选取导热性能更好的材料。

2.提高功率循环中结温测量的准确性。高性能功率器件带来不可忽视的结温梯度,但目前功率循环试验中的常用的结温测量方式得到的都是平均结温。为了更好的研究器件失效的过程,有必要设计一种可以在线准确获得结温梯度的方法。

3.研究新型封装结构的失效机理。关于新型封装结构失效机理的研究尚不多见,对其进行相应研究有利于为新封装结构的应用和改进提供思路。

分析多方面因素综合作用下的功率器件失效过程和机理。半导体模块在实际的工作中不仅涉及热应力,同时还受振动、湿度等因素影响,现有研究主要集中在温度对器件可靠性的影响,较少分析多种因素共同作用下的失效机理。半导体封装可靠性相关理论基础还不完善,目前还属于先设计再模拟,最后测试的传统研发流程,确定一个新的、更高性能的封装方式试错成本比较高,全流程可靠性数字化是半导体制造商急需的,侧面表现出半导体封装可靠性研究的重要性。