简介

在先进工艺节点中,无源器件和互连结构的电磁仿真对IC设计人员来说是一个巨大的挑战。而要解决这些挑战,以下几个技术是最常被探讨的:一个整合的设计环境,使电磁仿真工具能够无缝接入现有的设计平台中;在设计阶段中实现快速无源器件建模和合成;在签核sign-off 阶段实现精确验证,同时能把封装的影响考虑进来。

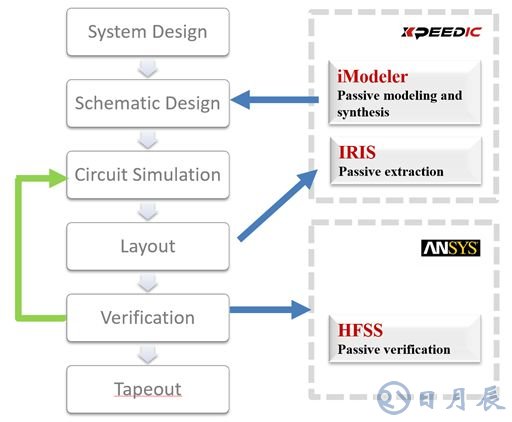

在本文中,演示了IRIS-HFSS整合流程,它无缝地集成在Cadence Virtuoso平台中(如图1所示)。在设计阶段,IRIS和iModeler采用加速矩量法(MOM)引擎和人工神经网络(ANN)技术,实现了快速无源器件仿真和合成;在签核阶段,把HFSS集成进来实现精确验证以及芯片封装联合仿真。

Figure1 Combined IRIS-HFSS flow for IC designers

集成在Virtuoso中的IRIS

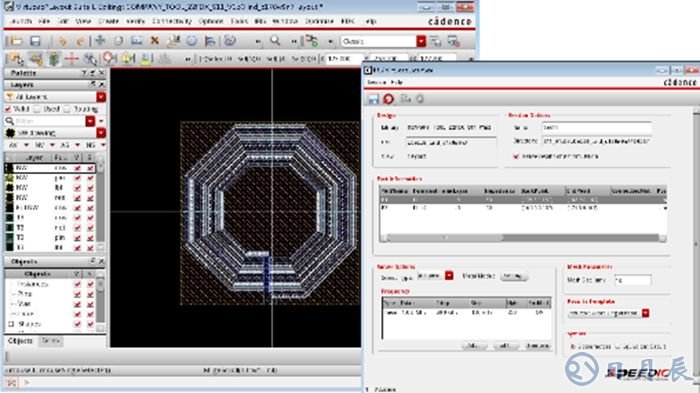

IRIS为IC设计人员提供了一种在主流设计环境中运行复杂的3D EM分析的简单方法。IRIS基于加速矩量法(MoM)的全波电磁求解器引擎已在多个先进工艺节点上验证了其准确性。Virtuoso无缝集成的形式避免了在设计环境和仿真环境之间转换时可能出现的各种问题,使得IC设计人员可以采用自动化的方式实现EM分析。

Figure2 Virtuoso-integrated IRIS interface

支持先进工艺节点

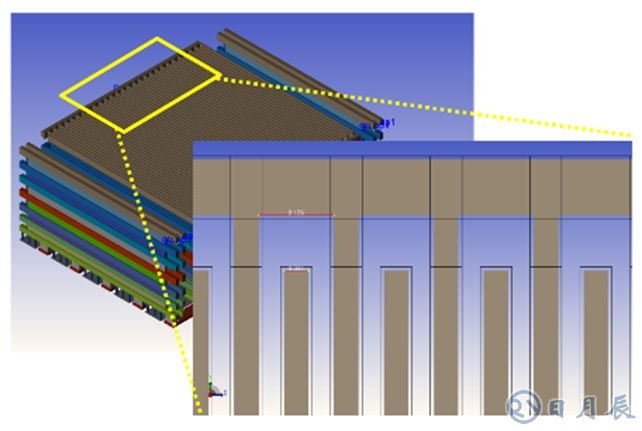

先进工艺节点对EM精确仿真提出了巨大挑战。先进工艺中线宽和线距的变化对金属电阻率(rho-table)和布局效应(bias-table)比较敏感,这对仿真精确度是至关重要的。举例来说,如果不考虑bias-table效应,momcap的电容值可能被低估超过20%。IRIS支持晶圆厂工艺文件中定义的rho-table和bias-table,以实现无源器件的精确建模和仿真结果。

Figure3 Width-and-spacing effect on a momcap

IRIS-to-HFSS

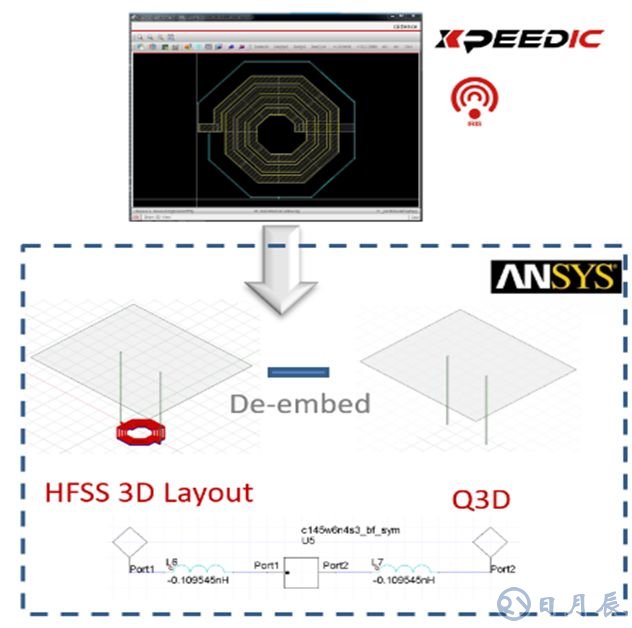

IRIS-to-HFSS接口为IC设计人员提供了一种途径,可以使用行业标准的HFSS来验证他们的无源模型。通过自动化的IRIS-to-HFSS接口,可以简化HFSS项目的建立,它不仅提供了IRIS内置的功能,如rho-table、bias-table和via defeaturing,而且还提供了HFSS的一些相关特性,如自动薄层合并、端口定义和Q3D去嵌等。通过在HFSS 3D Layout中导出,还可以实现芯片与封装的协同仿真。IRIS-HFSS流程已通过多个晶圆厂工艺节点认证。

Figure4 IRIS-to-HFSS interface

结论

本文演示了IRIS-HFSS整合流程,此流程涵盖了高级工艺节点上的设计和验证的整个过程, 它可以显著缩短IC设计人员的设计周期。

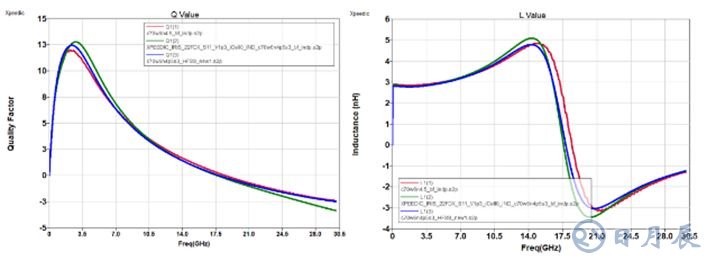

Figure5 IRIS,HFSS and Measurement Correlation